보내는 기사

"기술 밀리면 끝"…삼성전자, TSMC 이어 차세대 '반도체 패키지' 기술 개발

이미 가입된 회원입니다.

만 14세 이상만 회원으로 가입하실 수 있습니다.

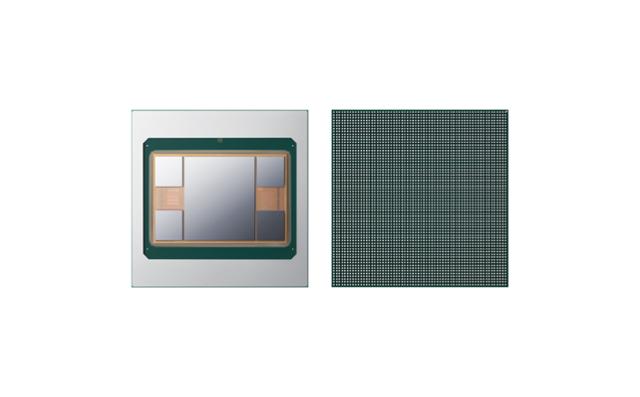

삼성전자가 로직 칩과 4개의 HBM 칩을 패키지로 구현한 독자 구조의 2.5D 차세대 패키지 기술 'I-Cube4'를 개발했다고 6일 밝혔다. 사진=삼성전자

삼성전자가 대만의 TSMC에 이어 '차세대 반도체 패키지' 기술 개발에 성공했다. 컴퓨터(PC) 중앙처리장치(CPU)와 같은 로직 칩에 고대역폭 메모리(HBM) 4개를 하나로 묶어 성능을 높인 기술로, 전송 속도는 높이면서도 패키지 면적은 줄인 게 특징이다. 업계에선 삼성전자가 하반기 중 초고난도인 HBM 6개를 끼워 넣는 기술도 선보일 것으로 예상한다. 반도체 수요 급증으로 반도체 위탁생산(파운드리) 분야가 호황을 맞이한 가운데 업계 선두인 TSMC와 삼성전자 간 기술 경쟁도 갈수록 치열해지는 양상이다.

삼성전자는 6일 로직 칩과 4개의 HBM 칩을 하나의 패키지로 구현한 2.5D 패키지 기술 'I-CUBE4'를 개발했다고 밝혔다.

최근 반도체 업계에선 4차 산업혁명을 선도할 반도체 핵심 기술로 '패키지 기술'이 떠오르고 있다. 기존엔 주로 D램, 낸드플래시, CPU처럼 각각 고유의 성능을 가진 반도체 칩 형태로만 공급됐다. 하지만 개별 반도체의 성능을 무한정 끌어올리기란 불가능에 가깝다. 현재 개발된 3나노미터(㎚·1㎚=10억 분의 1m) 기술도 높은 난이도로 '꿈의 공정'으로 꼽히는데, 이를 계속 줄이기란 쉽지 않다.

삼성전자 반도체 생산 공장에서 한 직원이 방진복을 입은 채 근무 중이다. 삼성전자 제공

이런 한계를 극복할 수 있게 도와주는 장치가 바로 '패키지 기술'이다. 쉽게 말해, 로직 칩과 슈퍼컴퓨터용 D램인 HBM을 미세회로 기판(인터포저)에 배치해 하나의 칩처럼 작동하게 하는 것이다. 반도체 미세공정이 선폭을 줄이는 게 기술 경쟁력의 핵심이라면, 패키지 기술은 같은 크기의 기판에 로직 칩과 얼마나 많은 HBM을 끼워 넣을 수 있느냐가 관건이다.

실제 초고속 데이터를 분석하는 슈퍼컴퓨터(HPC) 분야를 중심으로 첨단 패키지 기술의 중요성은 갈수록 높아지고 있다. HPC 성능을 끌어올리려면 고성능 시스템반도체가 필요한데, 이를 한 번에 해결할 반도체를 만들어내기란 쉽지 않다. 파운드리로선 첨단 미세공정만큼이나 첨단 패키지 기술을 확보하는 게 필수다.

삼성전자는 2018년 로직 칩과 2개의 HBM을 끼워 넣은 기술을 개발한 데 이어 이번에 3년여 만에 HBM 4개까지 끼워 넣는 패키지 기술을 개발했다. 현재 반도체 패키지 기술의 최강자는 TSMC로, 이미 HBM 6개를 탑재하는 기술까지 확보한 것으로 알려졌다.

시각물_TSMC 공정별 매출 구성.

삼성전자가 이번에 'I-CUBE4' 기술 개발 성공 소식을 발표한 것도 기술 경쟁에서 TSMC에 밀리지 않겠다는 의지로 보인다. 한 업계 관계자는 "삼성전자 내부에선 기술 경쟁에서 밀리면 TSMC를 따라잡는 게 어려울 것이란 위기감이 팽배하다"며 "한발 늦긴 했지만 이번에 차세대 패키지 기술 개발에 성공한 건 의미가 크다"고 말했다.

업계에선 삼성전자가 연내 HBM을 6개까지 끼워 넣는 기술도 선보일 것으로 전망하고 있다. 기술적인 측면에선 TSMC와 동일한 수준까지 올라간 셈이다. 강문수 삼성전자 파운드리사업부 전무는 "HBM을 6개, 8개 탑재하는 신기술도 개발해 시장에 선보이겠다"고 말했다. 삼성전자는 지난해 역대 최대인 10조 원가량을 쏟아부은 파운드리 사업에 올해는 더 많은 투자에 나설 것으로 알려졌다.

삼성전자는 지난해 8월 세계 최대 규모의 반도체 공장인 평택 2라인 가동에 들어갔다. 이 라인에서는 EUV(Extreme Ultraviolet, 극자외선) 공정을 적용한 첨단 3세대 10나노급(1z) LPDDR5 모바일 D램이 생산된다. 사진은 평택 2라인. 사진=연합뉴스

다만 TSMC 역시 '초격차'를 위해 역대 최대 투자를 예고한 상태다. 최근 일본 니혼게이자이신문(닛게이)은 "삼성전자가 올해 41조 원가량의 투자를 예고했지만 절반 이상이 메모리에 투자돼 TSMC와 비교하면 투자 규모가 떨어진다"며 "삼성전자와 TSMC의 격차가 점점 더 벌어지고 있다"고 전했다.

신고 사유를 선택해주세요.

작성하신 글을

삭제하시겠습니까?

로그인 한 후 이용 가능합니다.

로그인 하시겠습니까?

이미 공감 표현을 선택하신

기사입니다. 변경을 원하시면 취소

후 다시 선택해주세요.

구독을 취소하시겠습니까?

해당 컨텐츠를 구독/취소 하실수 없습니다.

댓글 0